I'm trying to create connection from BCD to 7-segment decoder.When I press button UP. or DOWN., it should counting up or counting down. But my simulation only displays 0000001 even when I press button UP or DOWN.BCD module code: module BCDcountmod(input Clock, Clear, up, down,output reg 3:0 BCD1,output reg 3:0 BCD0);//reg 3:0 BCD11, BCD00;always @(posedge Clock or negedge Clear) begin//- IS IT CLEAR?

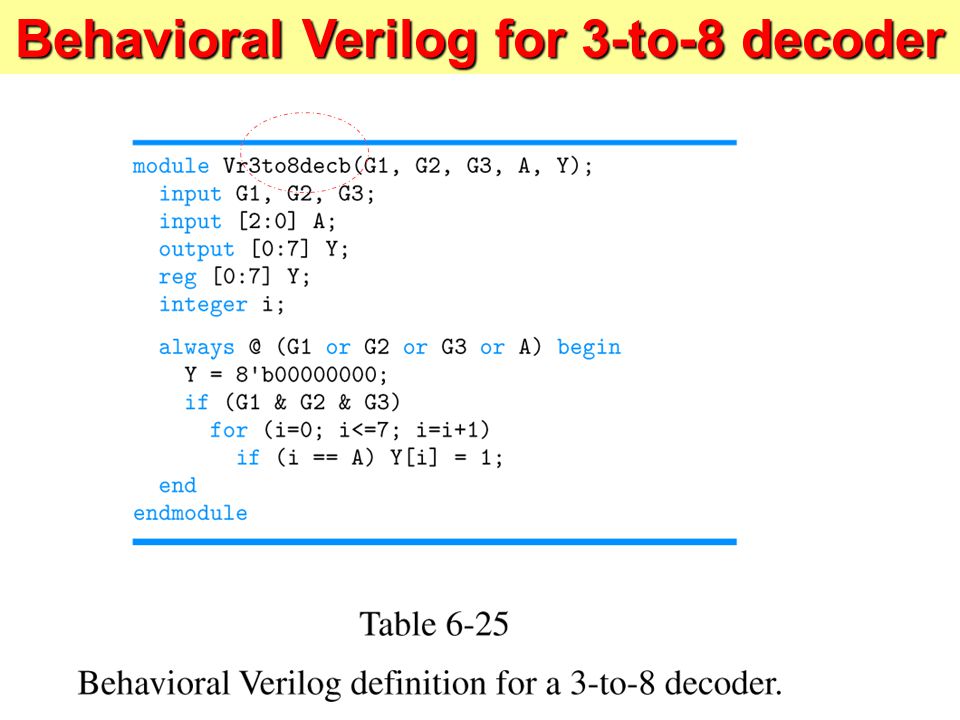

Verilog Behavioral Programs for logic gates implementation; Verilog Behavioral Program for Multiplexers; Verilog Behavioral Program for Flip Flops; Verilog Behavioral Program for Decoder; Python code to find the probability of drawing an ace or a heart from a pack of 52 playing cards; Verilog Behavioral Program for Counters. EE577b Verilog for Behavioral Modeling Nestoras Tzartzanis 6 February 3, 1998 Verilog Behavioral Language. Structures procedures for sequential or concurrent execution. Explicit control of the time of procedure activation specified by both delay expressions and by value changes called event expressions. Verilog - Modules The module is the basic unit of hierarchy in Verilog I Modules describe: I boundaries module, endmodule I inputs and outputs ports I how it works behavioral or RTL code I Can be a single element or collection of lower level modules I Module can describe a hierarchical design (a module of modules) I A module should be contained within one le.

-if (Clear) beginBCD1. General entry level debugging procedure.

Always run code in simulation before loading it onto a FPGA. Determiner which module has a bug(s):. Make sure the stimulus for the module matches your intentions.

Make sure the output for a module makes sense for its input. Step through line-by-line:. Make sure each branch is reachable and executing as intended. Dump everything in the debug scope into waveform. Add debug messages using $display. Add small delays such as #0.1 into the design.

2 To 4 Decoder Verilog Code Behavioural

This may require changing the time precision of the time scale. After the potential bug is found:. Correct it and add a note on the same line with a searchable keyword (ex: //FIXED). Run simulation to validate the fix. If the bug seems resolved. Comment-out (not remove) the debug messages and injected delays.

Run simulation again. Repeat step 4 until all the bugs are resolved. It is now safe to remove the commented-out messages and delays. RUN SIMULATION AGAIN!Hint:There is one design bug and one potential test bench issue. The stimulus you are using is not consistent with how you designed your module to work.

16 To 1 Multiplexer Verilog Code

The problem is in your testbench. Since this is homework I'll let you take it from there.EDIT: I'm going to assume that the homework deadline has passed. For the benefit of future readers, note that the Verilog module uses an active-low Clear signal that resets everything when it is at a logic 0. The testbench incorrectly assumes an active-high Reset signal, so Reset (and hence Clear) are being held low for almost the entire testbench. There's no way the Verilog module can do anything useful.it's being continuously cleared.

Gta san andreas mods steam pc. I'm asking this because GTA 5 doesn't run well on my PC so I'm probably going to return it and get GTA San Andreas + GTA 4, but I heard that. Heres something why you shouldnt buy GTA SA in Steam. Is make mods compatible to steam version, or something,I'm not really sure. Are you ready to be a Time Lord and save another day of San Andreas? In GTA V, if Michael/Trevor/Franklin get wasted, upon respawning from the hospital, they'll lose $5,000. Do you like the idea of winning a £25 Steam Gift Card? Apr 27, 2013 - How to install mods for the Gta San Andreas on the Steam because i dont find the local to install it. Five years ago Carl Johnson escaped from the pressures of life in Los Santos, San Andreas. A city tearing itself apart with gang trouble, drugs and corruption.